### **User Manual**

## **Tektronix**

VX4801 Programmable Digital I/O Module 070-9153-03

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) years from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### **EC Declaration of Conformity**

We

Tektronix Holland N.V. Marktweg 73A 8444 AB Heerenveen The Netherlands

declare under sole responsibility that the

#### VX4801

meets the intent of Directive 89/336/EEC for Electromagnetic Compatibility. Compliance was demonstrated to the following specifications as listed in the Official Journal of the European Communities:

EN 55011 Class A Radiated and Conducted Emissions

EN 50081-1 Emissions:

EN 60555-2 AC Power Line Harmonic Emissions

EN 50082-1 Immunity:

IEC 801-2 Electrostatic Discharge Immunity

IEC 801-3 RF Electromagnetic Field Immunity

IEC 801-4 Electrical Fast Transient/Burst Immunity

IEC 801-5 Power Line Surge Immunity

To ensure compliance with EMC requirements this module must be installed in a mainframe which has backplane shields installed which comply with Rule B.7.45 of the VXIbus Specification. Only high quality shielded cables having a reliable, continuous outer shield (braid & foil) which has low impedance connections to shielded connector housings at both ends should be connected to this product.

#### PROGRAMMING

The programming examples in the manual (see Section 4) are written in Microsoft GW BASIC, using the following commands.

#### CALL ENTER (R\$, LENGTH%, ADDRESS%, STATUS%)

Inputs data into the string R\$ from the IEEE-488 instrument whose decimal primary address is in the variable ADDRESS%. LENGTH% = the number of bytes read from the instrument. STATUS% = '0' if the transfer was successful or an '8' if an operating system timeout occurred in the PC. To use the CALL ENTER statement, the string R\$ must be set to a string of spaces whose length is greater than or equal to the maximum number of bytes expected from the VX4801.

#### CALL SEND (ADDRESS%, OUT\$, STATUS%)

Outputs the contents of the string variable OUT\$ to the IEEE-488 instrument whose decimal primary address is in the variable ADDRESS%. The variable STATUS% is a '0' if the transfer was successful and an '8' if an operating timeout occurred in the PC.

- END Terminates the program.

- FOR/NEXT Repeats the instructions between the FOR and NEXT statements for a defined number of iterations.

- GOSUB n Runs the subroutine beginning with line n. The end of the subroutine is marked with a RETURN statement. When the subroutine reaches the RETURN statement, execution will resume on the line following the GOSUB command.

- GOTO n Program branches to line n.

- IF/THEN Sets up a conditional IF/THEN statement. Used with other commands, so that IF the stated condition is met, THEN the command following is effective.

- REM or ' All characters following the REM command or a ' are not executed.

- RETURN Ends a subroutine and returns operation to the line after the last executed GOSUB command.

- <CR> Carriage Return character, decimal 13.

- <LF> Line Feed character, decimal 10.

## VX4801 PROGRAMMABLE DIGITAL I/O MODULE QUICK REFERENCE GUIDE

Numbers in parentheses refer to the page(s) in the Operating Manual.

SETUP Be sure all switches are correctly set. (p. 1 - 4)

Follow Installation guidelines. (p. 2 - 1)

The default condition of the VX4801 Module after the completion of power-up self test is as follows:

All I/O pins tri-stated All bytes defined as inputs, active high All external handshake lines disabled Request True interrupts disabled

LEDs When lit, the LEDs indicate the following:

Power power supplies functioning

| FUWE   | t power supplies functioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Failed | l module failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MSG    | module is processing a VMEbus cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RFI    | a VXI backplane interrupt is requested                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RFD    | the external device strobes ready for data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DAV    | Data AVailable line is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DRD    | the external device strobes data ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | Communication of the Communica |

DAK Data AcKnowledge line is low

ERR a programming error has occurred

I/O the current byte is programmed as an output

TRI the current byte is tri-stated

B7-B0 indicate the state of each bit of the currently displayed byte. Lit indicates the bit is high (TTL logic "1")

BYTE indicate which of the six bytes the bit LEDs (B7-B0 LEDs) are currently displaying, as follows:

| Byte     | LED status: |        |        |

|----------|-------------|--------|--------|

| Selected | Byte 2      | Byte 1 | Byte O |

| 0        | unlit       | unlit  | unlit  |

| 1        | unlit       | unlit  | lit    |

| 2        | unlit       | lit    | unlit  |

| 3        | unlit       | lit    | lit    |

| 4        | lit         | unlit  | unlit  |

| 5        | lit         | unlit  | lit    |

|          |             |        |        |

1

#### SYSTEM COMMANDS

The following VXIbus Instrument Protocol non-data commands are initiated by the VX4801's commander and will affect the module:

CLEAR - The module clears its VXIbus interface and any pending commands. Current module operations are unaffected.

TRIGGER - The trigger command has no effect on the VX4801 card.

BEGIN NORMAL OPERATION - The module will begin operation if it has not already done so.

READ PROTOCOL - The module will return its protocol to its commander.

READ STATUS - The module will return its status to its commander.

#### COMMAND SYNTAX

Command protocol and syntax for the VX4801 Module is as follows:

- Each command consists of a string of up to 255 characters. Every command <u>must</u> end with either a line feed <LF> or a semi-colon (;) delimiter. A <CR> is treated as a white space character, and is ignored if received.

- All commands are operated on in the order they are received, and executed when the delimiter is received.

- 3) If a given parameter is omitted within a command, either its default state or its last programmed state will be in effect (depending on the particular command issued).

- 4) Any character may be sent in either upper or lower case form.

- 5) Any of the following white space characters are allowed within the command string, and are ignored by the module:

00-09, 08-20; 80-89, 88-90

- 6) Any command syntax or programming errors will cause the command to be ignored, and an error will be flagged. All commands up to the occurrence of the error will remain valid. The invalid command and all subsequent commands will be lost, and no commands will be accepted until the error condition is cleared.

- 7) All responses from the module are terminated by a carriage return and line-feed <CR><LF>.

#### MODULE COMMANDS

- specifies which bytes are to be read, the order in which they are to be read (and reported), and any masks to be overlaid onto the data prior to reporting it. Returns ASCII hex data representing all input bytes, selected input and/or output bytes, or selected bits of a byte (by using a mask). (3 5)

- specifies the data to be output, the order of output, and any masks to be overlaid onto the data prior to output. The ASCII hex data representing all output bytes, selected output bytes, single bits of a byte, or mask overlays onto the byte(s) can be used to update the cards' output data latches. (3 8)

- M command defines which bytes are inputs and which are outputs, and their active logic sense (active high true or active low true). (3 12)

- P specifies the active edge of the handshake signals (positive or negative edge triggered). (3 14)

- Q reads the current state of the module: (3 15)

error data; the state of the external handshake lines (DRD,RFD); the

current tri-state condition of the I/O latches; the programmed I/O

configuration; the programmed active edges of the handshake

signals, and whether the handshake(s) are active; the programmed

logic sense of each latch; the programmed external tri-state level of

each latch.

- R resets the board to its power-up state. (3 18)

- S executes a self test, and then returns to its power-up state. (3 19)

- specifies whether output bytes are tri-stated (high-impedance), or active.

This command is logically OR'ed with the external tri-state lines. (3 20)

- U specifies the conditions for which the inputs and outputs are updated (update on command, or update on external handshake control). (3 21)

- VER returns the current software revision level of the board. (3 23)

- X enables or disables the VXI Request True interrupt. This interrupt can be programmed to be active when an error occurs, when either external handshake is valid (DRD,RFD), or when any combination of the three occurs. (3 24)

- Z specifies the active level of the external tri-state control lines ETSO, ETS5 ETS9 (active high true or active low true). (3 25)

### **Table of Contents**

|      | tion 1                                       |

|------|----------------------------------------------|

| Gen  | eral Information and Specifications          |

|      | Introduction                                 |

|      | Controls And Indicators                      |

|      | Switches                                     |

|      | Fuses                                        |

|      | LEDs 1 – 6                                   |

|      | BITE (Built-In Test Equipment)               |

|      | Glossary 1 – 9                               |

|      | Specifications                               |

| Sect | tion 2                                       |

| Prep | paration For Use                             |

|      | Installation Requirements And Cautions       |

|      | Installation Procedure                       |

|      | Installation Checklist                       |

| Sect | tion 3                                       |

| Ope  | ration                                       |

| -    | Overview                                     |

|      | Power-up                                     |

|      | System Commands                              |

|      | Module Operation                             |

|      | Command Syntax                               |

|      | Command Summary                              |

|      | Command Descriptions 3 – 5                   |

|      | SYSFAIL, Self Test, and Initialization       |

| Sect | tion 4                                       |

|      | gramming Examples                            |

|      | Definition of BASIC Commands 4 – 1           |

|      | Programming Example In BASIC                 |

|      |                                              |

| App  | endices                                      |

|      | Appendix A – VXIbus Operation A – 1          |

|      | Appendix B - Input/Output Connections        |

|      | Appendix C – VXI Glossary A – 9              |

|      | Appendix D – User Service                    |

|      | Appendix E – Performance Verification A – 19 |

VX4801 i

### **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

#### **Injury Precautions**

**Avoid Electric Overload** To avoid electric shock or fire hazard, do not apply a voltage to a terminal that is

outside the range specified for that terminal.

**Do Not Operate Without** To avoid electric shock or fire hazard, do not operate this product with covers or

**Covers** panels removed.

**Use Proper Fuse** To avoid fire hazard, use only the fuse type and rating specified for this product.

**Do Not Operate in**To avoid electric shock, do not operate this product in wet or damp conditions.

Wet/Damp Conditions

**Do Not Operate in an**To avoid injury or fire hazard, do not operate this product in an explosive

**Explosive Atmosphere** atmosphere.

#### **Product Damage Precautions**

**Provide Proper Ventilation** To prevent product overheating, provide proper ventilation.

**Do Not Operate With**Suspected Failures

If you suspect there is damage to this product, have it inspected by qualified service personnel.

#### **Safety Terms and Symbols**

**Terms in This Manual**

These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

**Terms on the Product**

These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product

The following symbols may appear on the product:

DANGER High Voltage

Protective Ground (Earth) Terminal

ATTENTION Refer to Manual

Double Insulated

#### **Certifications and Compliances**

Overvoltage Category

Overvoltage categories are defined as follows:

CAT III: Distribution level mains, fixed installation

CAT II: Local level mains, appliances, portable equipment

CAT I: Signal level, special equipment or parts of equipment, telecommunication, electronics

## VX4801 Programmable Digital I/O Module

# Section 1 General Information and Specifications

#### Introduction

The VX4801 Module is a printed circuit board assembly for use in a mainframe conforming to the VXIbus Specification, such as the VX1400 or VX1401 "C" size mainframe used in the Tek/CDS IAC System. The VX4801 provides 48 optically isolated TTL- or CMOS-compatible bidirectional digital I/O lines.

The VX4801 is especially useful in applications which require isolation between the UUT (Unit Under Test) and the test equipment. This is often the case when the possibility exists of a ground loop between the UUT and the test station ground. This can occur when the UUT has its own floating power source, as is often the case in space-craft components or sub-assemblies.

The 48 programmable I/O signal lines are organized as six 8-bit bytes. Each of the six bytes can be independently configured under full program control. All commands and responses are in ASCII hex notation for ease of programming, and to insure compatibility with the widest range of systems controllers. Program controlled parameters include:

- selection of any byte as either input or output

- definition of masks for input and output data

- latch input data or control output data on software command basis or on external handshake

- logic sense of input, output and handshake lines

- full reporting of operating parameters at any time

The data output can be controlled as bits, as individual bytes, and as groups of bytes. Output is controlled on a command basis, or on a qualified basis using external handshakes.

VX4801 1 - 1

Data input is also fully under program control. The module can report the state of all input bytes, groups of input and/or output bytes, and single bits of a byte. Input data can be updated on a command request basis, or on a qualified basis using external handshakes.

User-defined masks can be overlaid on the data prior to output. Masks may also be applied to individual input bytes before they are returned to the system controller to improve data post-processing speed and ease of data interpretation.

The sense of inputs, outputs, and handshake lines can be set to either active high or active low under program control. The active edge can also be programmed for handshake lines. All I/O lines are both TTL and CMOS compatible, with up to 24 mA of sink current provided for each output. The I/O section of the module is fully isolated from system ground using opto-isolators and an isolated power supply contained on the module.

External (handshake) control signals are provided for output and input data control. Output data control signals are Ready For Data (RFD), Data Available (DAV), and External Tri-State control (ETSO - ETS5). Input data control signals are Data Ready (DRD) and Data Acknowledge (DAK).

The VX4801 provides full access to system status information, which is especially helpful during system trouble-shooting, software de-bugging, and operational system checks. At any time, the system controller can read the state of the external handshake lines, the programmed I/O configuration, the programmed active edges of all handshake signals, which handshake signals are active, the programmed logic sense of each I/O byte, the tri-state condition of each output byte, and up-to-date error data.

Built-in-Test-Equipment (BITE) is provided on the module by an internal loop-back path that allows the module to be tested with its outputs tri-stated, verifying I/O paths for each byte. A self test is automatically performed on power up, or upon command. Front panel LEDs indicate the status of power, assertion of the VMEbus signal SYSFAIL\*, backplane cycles, data handshake signals, and individual I/O bits. In addition, the Query command can be used to determine the current state of the module during operation.

Note that certain terms used in this manual have very specific meanings in the context of a VXIbus System. These terms are defined in the VXIbus Glossary (Appendix C).

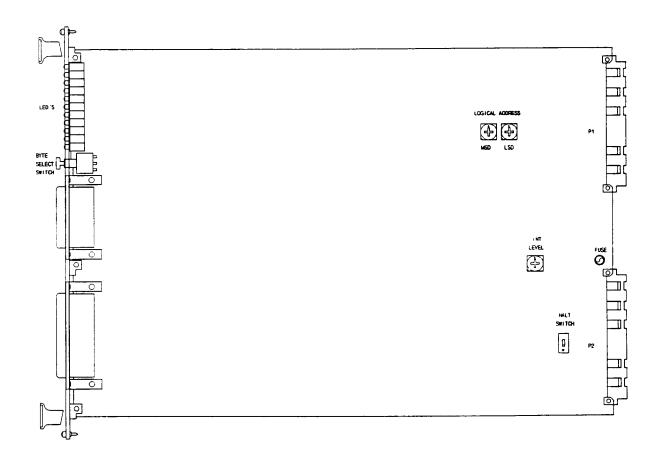

Figure 1: VX4801 Controls and Indicators

VX4801 1 - 3

#### **Controls And Indicators**

The following controls and indicators are provided to select and display the functions of the VX4801 Module's operating environment. See Figures 1 and 2 for their physical locations.

#### **Switches**

#### Logical Address Switches

LOGICAL ADORESS

MSD LSD

Each function module in a VXIbus System must be assigned a unique logical address, from 1 to 255 decimal. The base VMEbus address of the VX4801 is set to a value between 1 and FFh (255d) by two <a href="https://example.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hexample.com/hex

The actual physical address of the VX4801 Module is on a 64 byte boundary. If the switch representing the most significant digit (MSD) of the logical address is set to position X and the switch representing the least significant digit (LSD) of the logical address is set to position Y, then the base physical address of the VX4801 will be [(64d \* XYh) + 49152d]. For example:

M L

L. S S Base Physical

A. D D Addr. (d)

Ah 0 A (64\*10)+49152 = 49792d 15h 1 5 (64\*21)+49152 = 50496d

where: L.A. = Logical Address

MSD = Most Significant Digit

LSD = Least Significant Digit

#### IEEE-488 Address

Using the VX4801 Module in an IEEE-488 environment requires knowing the module's IEEE-488 address in order to program it. Different manufacturers of IEEE-488 interface devices may have different algorithms for equating a logical address with an IEEE-488 address.

If the VX4801 is being used in a Tek/CDS IEEE-488 IAC system, consult the operating manual of the Tek/CDS Resource Manager/IEEE-488 Interface Module being used.

If the VX4801 is being used in a MATE system, VXIbus logical addresses are converted to IEEE-488 addresses using the algorithm specified in the MATE IAC standard (MATE-STD-IAC). This algorithm is described in detail in the 73A-156 Operating Manual.

If the VX4801 is not being used in a Tek/CDS IAC System, consult the operating manual of the IEEE-488 interface device being used for recommendations on setting the logical address.

#### VMEbus Interrupt Level Select Switch

Each function module in a VXIbus System can generate an interrupt on the VMEbus to request service from the interrupt handler located on its commander (for example, the VX4520 Slot 0 Device/Resource Manager in a VX7401 IEEE-488 Interface System). The VMEbus interrupt level on which the VX4801 Module generates interrupts is set by a BCD rotary switch. Align the desired switch position with the arrow on the module shield.

Valid Interrupt Level Select Switch settings are 1 through 7, with setting 1 equivalent to level 1, etc. The level chosen should be the same as the level set on the VX4801's interrupt handler, typically the module's commander. Setting the switch to an invalid interrupt level (0, 8, or 9) will disable the module's interrupts.

Interrupts are used by the module to return VXIbus Protocol Events to the module's commander. Refer to the <u>Operation</u> section for information on interrupts. The VXIbus Protocol Events supported by the module are listed in the <u>Specifications</u> section.

#### Halt Switch

This two-position slide switch selects the response of the VX4801 Module when the Reset bit in the module's VXIbus Control register is set.

If the Halt switch is in the ON position, the VX4801 Module is reset to its power-up state and all programmed module parameters are reset to their default values.

If the Halt switch is in the OFF position, the module will ignore the Reset bit and no action will take place.

Note that the module is not in strict compliance with the VXIbus Specification when the Halt switch is OFF.

Control of the Reset bit depends on the capabilities of the VX4801's commander. With a Tek/CDS VX4521, for example, the Reset bit is set if the VX4521 is programmed with a RESET command via the IEEE-488 bus.

#### Byte Select Switch

The Byte Select Switch located on the front panel is a momentary action switch that controls which of the six I/O bytes is currently being displayed on the LEDs. Each time the switch is depressed, the state of the next byte in sequence is displayed on the LEDs. For example, if the state of byte 0 is currently displayed, the state of byte 1 will be displayed after the switch is depressed. The BYTE LEDs will display the number of the selected byte (see BYTE in the listing of LEDs below).

#### **Fuses**

The VX4801 Module has a single +5V fuse. The fuse protects the module in case of an accidental shorting of the power bus or any other situation where excessive current might be drawn.

If the +5V fuse opens, the VXIbus Resource Manager will be unable to assert SYSFAIL INHIBIT on this module to disable SYSFAIL\*.

If the +5 V fuse blows, remove the fault <u>before</u> replacing the fuse. Replacement fuse information is given in the <u>Specifications</u> section of this manual. Figure 1 shows the location of this fuse on the VX4801 Module.

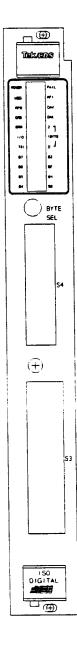

#### **LEDs**

The following LEDs are visible at the top of the VX4801 Module's front panel to indicate the status of the module's operation:

#### **POWER LED**

This green LED is normally lit and is extinguished if the +5V power supply fails, or if the +5V fuse blows.

#### **FAIL LED**

This normally off red LED is lit whenever SYSFAIL\* is asserted, indicating a module failure. Module failures include failure to correctly complete a self test, loss of a power rail, or failure of the module's central processor.

If the module loses any of its power voltages, the Failed LED will be lit and SYSFAIL\* asserted. A module power failure is indicated when the module's Power LED is extinguished.

#### MSG LED

This green LED is normally off. When lit, it indicates that the module is processing a VMEbus cycle. The LED is controlled by circuitry that appears to stretch the length of the VMEbus cycle. For example, a five microsecond cycle will light the LED for approximately 0.2 seconds. The LED will remain lit if the module is being constantly addressed.

#### RFI

Request for Interrupt. This LED lights when a VXI backplane interrupt is requested. Like the MSG LED, the pulse width is stretched to make it visible.

#### **RFD**

Indicates the state of the Ready for Data handshake signal. This LED lights when the external device strobes ready for data indicating it is ready for more data. It is cleared when new data is output by the module.

#### DAV

Indicates the level of the Data Available handshake signal. This LED lights when the DAV line is low. It clears when the DAV line goes high.

1 - 6 VX4801

#### DRD

Indicates the state of the Data Ready handshake signal. This LED lights when the external device strobes data ready indicating new input data is valid. It is cleared when the controller reads the input data.

#### DAK

Indicates the level of the Data Acknowledge handshake signal. This LED lights when the DAK line is low. It is cleared when the DAK line is high.

#### **BYTE**

Three LEDs that indicate which of the six bytes (0 through 5) the bit LEDs (B7-B0 LEDs) are currently displaying, as follows:

| Byte<br>Selected | Byte 2         | LED status:<br>Byte 1 Byt |     |

|------------------|----------------|---------------------------|-----|

| 0<br>unlit       | unlit          | unlit                     |     |

| 1 2              | unlit<br>unlit | unlit<br>lit              | lit |

| unlit            |                |                           |     |

#### **ERR**

Indicates a programming error has occurred. This LED will remain lit until the error condition is cleared.

#### 1/0

Indicates the programmed input/output state of the current byte being displayed. The LED is lit if the byte is programmed as an output, and unlit if programmed as an input byte.

#### <u>TRI</u>

Indicates the tri-state condition of the byte currently being displayed. A lit LED indicates the byte is tri-stated.

#### B7 - B0

Indicates the state of each bit of the currently displayed byte. The LED being lit indicates the bit is high (TTL logic 1). An unlit LED indicates the bit is low (TTL logic 0). B7 is the most significant bit, and B0 the least significant bit.

#### **BITE (Built-In Test Equipment)**

BITE is provided on the module by an internal loop-back path, which allows the module to be tested with the outputs tri-stated. The self test automatically tests and verifies all loop-back paths for each byte.

VX4801 1 - 7

Self test is automatically performed on power-up, and can also be commanded. All the outputs are checked with their corresponding inputs, and with the output drivers in tristate.

Front panel LEDs indicate the status of Power, assertion of the VMEbus signal SYSFAIL\*, backplane cycles, handshake signals, and other system operating parameters. In addition, the Query command can be used to determine the current state of the module during operation, including error codes (see the Query command in the <u>Command Descriptions</u> subsection).

Figure 2: VX4801 Front Panel

#### Glossary

A glossary of VXIbus terms is provided in Appendix C. In addition, the following terms specific to the VX4801 Module are defined:

#### External Handshake Controls

#### **Output Data:**

#### Ready For Data (RFD)

Ready For Data is an input from an external device indicating it is ready for data. This signal is programmable to be either positive or negative edge triggered true.

#### Data Available (DAV)

Data Available is an output to an external device indicating valid data is available on the outputs. This signal is programmable to be either positive or negative edge triggered true.

#### External Tri-State control (ETSO - ETS5)

Six external tri-state control lines are provided, one for each of the six bytes. These lines are inputs from an external device which cause the corresponding byte to go into tri-state (high impedance). The tri-state control lines are programmable to be either active high or active low.

#### Input Data Control:

#### Data Ready (DRD)

Data ready is an input from an external device indicating valid data is at the inputs. This signal is programmable to be either positive or negative edge triggered true.

#### Data Acknowledge (DAK)

Data acknowledge is an output to an external device indicating the input data has been accepted. This signal is programmable to be either positive or negative edge triggered true.

VX4801 1 - 9

#### **Specifications**

Number of I/O Channels:

48.

Configuration:

I/O lines selectable as input or output on an 8-bit byte basis. Also tri-

state programmable on an 8-bit byte basis.

Byte Transfer Polarity:

All input and output bytes individually selectable as active high or

active low.

Input Data:

Returned as two hexadecimal ASCII characters per byte.

Input Control:

On program command, or with external Ready For Data and Data

Available handshake.

**Output Data:**

Programmed as two hexadecimal ASCII characters per byte, or by an

H or L character on an individual bit basis.

Output Control:

On program command, or with external Data Ready and Data

Acknowledge handshake.

Tri-State Control:

On program command on an individual byte, or by individual external

tri-state control signals for each byte.

Mask Capability:

On an individual byte basis, for input or output. AND, OR, and XOR

masking provided.

Byte Ordering:

A predefined sequence for input or output byte transfer may be

programmed. Bytes may be transferred in any required order.

Interrupt Modes:

Program selectable, on programming error, Ready For Data

handshake, and/or Data Ready handshake.

**External Control**

Logic Sense:

Data Available, Ready For Data, Data Acknowledge, and Data Ready

control line polarities are all individually program selectable as low or

high true.

I/O Signal Type:

TTL and CMOS compatible (74AHCT245 driver).

1 - 10 VX4801

#### D.C. Electrical Characteristics:

|                                                                                                                                                                     | <u>min</u>  | <u>typ</u> | <u>max</u>        | <u>units</u>       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------------|--------------------|

| Output high voltage ( $V_{oh}$ ) $I_0 = -20 \mu A$ $I_0 = -6 m A$                                                                                                   | 4.4<br>3.84 | 5.0<br>4.2 |                   | V<br>V             |

| Output low voltage ( $V_{ol}$ ) $I_{o} = 20 \mu A$ $I_{o} = 24 m A$ Output low current ( $I_{ol}$ )                                                                 |             | 0          | 0.1<br>0.5<br>24  | V<br>V<br>mA       |

| Input high voltage (V <sub>ih</sub> )<br>Input low voltage (V <sub>il</sub> )<br>* Input current (I <sub>in</sub> )<br>Tri-state leakage current (I <sub>oz</sub> ) | 2.0         | 0.5        | 0.8<br>230<br>5.0 | V<br>V<br>μA<br>μA |

<sup>\*</sup> There are 22 k $\Omega$  pull-up resistors to + 5V on all I/O and handshake lines to account for floating inputs. The inputs IC use 1.0  $\mu$ A max, while the pull-down resistors require 5V / 22 k $\Omega$  = 227.6  $\mu$ A.

–10 ° to +55 ° C., typical specs at 25° C. A minus sign indicates current flowing out of the card.

Isolation Resistance:

> 100e6 ohms at 500V dc.

Isolation Voltage:

> 250V dc.

**External Control Lines:**

External Tri-state Input

30 nS typical.

to Tri-state Active:

63 nS maximum.

Valid Output Data to

Data Available Strobe:

0 nS.

Data Acknowledge to Data

Ready Strobe Delay:

0 nS.

**VXIbus Compatibility:**

Fully compatible with the VXIbus Specification for message-based

instruments with the Halt switch in the ON position.

VXI Device Type:

VXI message based instrument, Revision 1.4.

**VXI Protocol:**

Word serial.

VXI Module Size:

C size, one slot wide.

Module-Specific

Commands:

All module-specific commands and data are sent via the VXIbus Byte-Available command. All module-specific commands are made up of

ASCII characters. Module-specific data may be in either ASCII or

binary format.

VMEbus Interface:

Data transfer bus (DTB) slave - A16, D16 only.

VX4801 1 - 11

Interrupt Level:

Switch selectable, levels 1 (highest priority) through 7 (lowest).

Interrupt Acknowledge:

D16, lower 8 bits returned are the logical address of the module.

**VXIbus Data Rate:**

Write: 20 Kbytes/sec maximum. Read: 400 Kbytes/sec maximum.

**VXIbus**

Commands Supported:

All VXIbus commands are accepted (e.g. DTACK\* will be returned).

The following commands have effect on this module; all other

commands will cause an Unrecognized Command Event:

BYTE AVAILABLE (with or without END bit set)

BYTE REQUEST

**BEGIN NORMAL OPERATION**

READ PROTOCOL READ STATUS

**CLEAR**

\* GRANT DEVICE

\* TRIGGER

\* SET LOCK

\* CLEAR LOCK

\* IDENTIFY COMMANDER

\* These commands are accepted, but have no effect on the module.

VXIbus Protocol Events Supported:

VXIbus events are returned via VME interrupts. The following events are supported and returned to the VX4801 Module's commander:

REQUEST TRUE (In IEEE-488 systems such as the VX4801, this interrupt will cause a Service Request (SRQ) to be generated on the IEEE-488 bus.

**VXIbus Registers:**

ID

Device Type Status

Control Protocol Response Data Low

See Appendix A for definition of register contents.

Device Type

Register Contents:

F4DE (ones complement of binary value of model number with bit

11 set low).

**Power Requirements:**

All required dc power is provided by the Power Supply in the VXIbus

mainframe.

Voltage:

+5 Volt Supply: 4.75V dc to 5.25V dc.

## Section 2 Preparation For Use

#### Installation Requirements And Cautions

The VX4801 Module is a C size VXIbus instrument module and therefore may be installed in any C or D size VXIbus mainframe slot other than slot 0. If the module is being installed in a D size mainframe, consult the operating manual for the mainframe to determine how to install the module in that particular mainframe. Setting the module's logical address switch defines the module's programming address. Refer to the Controls and Indicators subsection for information on selecting and setting the VX4801 Module's logical address.

#### **Tools Required**

The following tools are required for proper installation:

Slotted screwdriver set.

Note that there are two printed ejector handles on the card. To avoid installing the card incorrectly, make sure the ejector marked "VX4801" is at the top.

In order to maintain proper mainframe cooling, unused mainframe slots must be covered with the blank front panels supplied with the mainframe.

Based on the number of instrument modules ordered with the mainframe, blank front panels are supplied to cover all unused slots. Additional VXIbus C size single-slot and C size double-slot blank front panels can be ordered from your Tektronix supplier.

Verify that the mainframe is able to provide adequate cooling and power with this module installed. Refer to the mainframe Operating Manual for instructions.

VX4801 2 - 1

If the VX4801 is used in a Tek/CDS VXI Series Mainframe, all VX4801 cooling requirements will be met.

#### Installation Procedure

The VX4801 Module is a piece of electronic equipment and therefore has some susceptibility to electrostatic damage (ESD). ESD precautions must be taken whenever the module is handled.

- Record the module's Revision Level, Serial Number (located on the label on the top shield of the VX4801), and switch settings on the Installation Checklist.

Only qualified personnel should install the VX4801 Module.

- Verify that the switches are switched to the correct values. The Halt switch should be in the ON position unless it is desired to not allow the resource manager to reset this module.

Note that with either Halt switch position, a "hard" reset will occur at power-on and when SYSRST\* is set true on the VXIbus backplane. If the module's commander is a VX4520 or VX4521 Slot 0 Device/Resource Manager, SYSRST\* will be set true whenever the Reset switch on the front panel of the VX4520 or VX4521 is depressed. Also note that when the Halt switch is in the OFF position, the module is not in strict compliance with the VXIbus Specification.

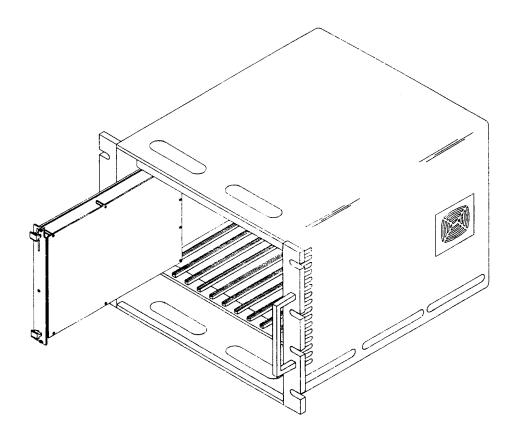

3) The module can now be inserted into any slot of the chassis other than slot 0.

If the VX4801 Module is inserted in a slot with any empty slots to the left of the module, the VME daisy-chain jumpers must be installed on the backplane in order for the VX4801 Module to operate properly. Check the manual of the mainframe being used for jumpering instructions.

If a Tek/CDS VX1400 or VX1401 Mainframe is being used, the jumper points may be reached through the front of the mainframe. There are five (5) jumpers that must be installed for each empty slot. The five jumpers are the pins to the <u>left</u> of the empty slot.

2 - 2 VX4801

Figure 3: Module Installation

#### 4) Installation of Cables:

If the module is being installed in a Tek/CDS VX1400 or VX1401 Mainframe, route the cables from the front panel of the module down through the cable tray at the bottom of the mainframe and out the rear of the mainframe. Connect the cable to the VX4801 Module's S4/S3 interface.

If a special cable is needed, 73A-657P and 73A-782P Hooded Connectors may be used to cable between the module's output connectors and the UUT.

VX4801 2 - 3

#### Installation Checklist

Installation parameters may vary depending on the mainframe being used. Be sure to consult the mainframe Operating Manual before installing and operating the VX4801 Module.

| Revision Level:                |       |

|--------------------------------|-------|

| Serial No.:                    |       |

| Mainframe Slot Number:         |       |

| Switch Settings:               |       |

| VXIbus Logical Address Switch: |       |

| Interrupt Level Switch:        | _     |

| Halt Switch:                   |       |

| Cabling Installed:             |       |

| S3 Cable:                      |       |

| S4 Cable:                      |       |

|                                |       |

|                                |       |

|                                |       |

|                                |       |

|                                |       |

|                                |       |

|                                |       |

|                                |       |

| Performed by:                  | Date: |

2 - 4 VX4801

## Section 3 Operation

#### Overview

The VX4801 Module provides 48 optically isolated TTL- or CMOS-compatible bidirectional digital I/O lines. The 48 programmable I/O signal lines are organized as six 8-bit bytes. Each of the six bytes can be independently configured under full program control. All commands and responses are in ASCII hex notation.

The data output can be controlled as bits, as individual bytes, and as groups of bytes. Output is controlled on a command basis, or on a qualified basis using external handshakes. Data input is also fully under program control. The module can report the state of all input bytes, groups of input and/or output bytes, and single bits of a byte. Input data can be updated on a command request basis, or on a qualified basis using external handshakes.

User-defined masks can be overlaid on the data prior to output. Masks may also be applied to individual input bytes before they are returned to the system controller.

The sense of inputs, outputs, and handshake lines can be set to either active high or active low under program control. The active edge can also be programmed for handshake lines. External (handshake) control signals are provided for output and input data control.

The VX4801 provides full access to system status information, which is especially helpful during system trouble-shooting, software de-bugging, and operational system checks.

The VX4801 Module is programmed by ASCII characters issued from the system controller to the VX4801 Module via the module's VXIbus commander and the VXIbus mainframe backplane. The module is a VXIbus Message Based instrument and communicates using the VXIbus Word Serial Protocol. Refer to the manual for the VXIbus device that will be the VX4801 Module's commander for details on the operation of that device.

#### Power-up

The VX4801 Module will complete its self test and be ready for programming five seconds after power-up. (Other modules in the VXIbus may require a longer power-up delay.) The Power LED will be on, and all other LEDs off. The MSG LED will blink during the power-up sequence as the VXIbus Resource Manager addresses all modules in the mainframe. The default condition of the module after power-up is described in the SYSFAIL, Self Test and Initialization subsection.

#### **System Commands**

Although these non-data commands are initiated by the VX4801's commander (for example, (for example, the VX4520 or VX4521 Module) rather than the system controller, they have an effect on the VX4801 Module. The following VXIbus Instrument Protocol Commands will affect the VX4801:

| Command         | Effect                                                                                                     |

|-----------------|------------------------------------------------------------------------------------------------------------|

| Clear           | The module clears its VXIbus interface and any pending commands. Current module operations are unaffected. |

| Trigger         | The trigger command has no effect on the VX4801 Module.                                                    |

| Begin Normal Op | eration  The module will begin operation if it has not already done so.                                    |

| Read Protocol   | The module will return its protocol to its commander.                                                      |

| Read Status     | The module will return its status to its commander.                                                        |

#### **Module Commands**

A summary of the VX4801's Module's commands is listed below. This is followed by detailed descriptions of each of the commands. A sample BASIC program using these commands is shown at the end of this section.

#### **Command Syntax**

Command protocol and syntax for the VX4801 Module is as follows:

- 1) Each command consists of a string of up to 255 characters. Every command must end with either a line feed (<LF>) or a semi-colon (;) delimiter. A <CR> is treated as a white space character, and is ignored if received.

- 2) All commands are operated on in the order they are received, and executed when the delimiter is received.

- 3) If a given parameter is omitted within a command, either its default state or its last programmed state will be in effect (depending on the particular command issued).

- 4) Any character may be sent in either upper or lower case form.

- 5) Any of the following white space characters, whose 8-bit hexadecimal values are given below, are allowed within the command string, and are ignored by the module:

3 - 2 VX4801

00-09, 0B-20 80-89, 8B-90

- 6) Any command syntax or programming errors will cause the command to be ignored, and an error will be flagged. All commands up to the occurrence of the error will remain valid. The invalid command and all subsequent commands will be lost, and no commands will be accepted until the error condition is cleared, either through a hardware or software reset, or by reading the error out with the O command.

- 7) All responses from the module are terminated by a carriage return and line feed <CR><LF>.

#### **Command Summary**

Detailed descriptions of each command (in alphabetical order) are given following the summary. An overview of the commands is as follows:

- The Input Data command specifies which bytes are to be read, the order in which they are to be read (and reported), and any masks to be overlaid onto the data prior to reporting it. ASCII hex data representing all input bytes, selected input and/or output bytes, or selected bits of a byte (by using a mask) can be returned to the system controller using this command.

- The Load Output command specifies the data to be output, the order of output, and any masks to be overlaid onto the data prior to output. The ASCII hex data representing all output bytes, selected output bytes, single bits of a byte, or mask overlays onto the byte(s) can be used to update the cards' output data latches.

- M The Mode command defines which bytes are inputs and which are outputs, and their active logic sense (active high true or active low true).

- P The Strobe Pulse Sense command specifies the active edge of the handshake signals (positive or negative edge triggered).

- Q The Query Status command is used to read the current state of the module. The information which can be obtained includes:

- error data:

- the state of the external handshake lines (DRD,RFD);

- the current tri-state condition of the I/O latches;

- the programmed I/O configuration;

- the programmed active edges of the handshake signals, and whether the handshake(s) are active;

- the programmed logic sense of each latch;

- the programmed external tri-state level of each latch.

- R The Reset command resets the board to its power-up state.

- S The Self Test command causes the module to execute a self test, and then return to its power-up state.

- The Tri-state Control command specifies whether the output bytes are tri-stated (high-impedance), or active. This command is logically OR'ed with the external tristate lines.

- U The Update command specifies the conditions for which the inputs and outputs are updated (update on command, or update on external handshake control).

VER The Version command returns the current software revision level of the board.

- X The X command is used to enable or disable the VXI Request True interrupt. This interrupt can be programmed to be active when an error occurs, when either external handshake is valid (DRD,RFD), or when any combination of the three occurs.

- Z The Tri-state Level command specifies the active level of the external tri-state control lines ETS0-ETS5 (active high true or active low true).

A detailed description of each command, in the same order as listed above, is given on the following pages. The syntax used in the command descriptions is:

- () optional parameter

- { } group of parameters

- ' ' ASCII character

- ... optional repetition

Note that the (),  $\{\}$ , '', and ... characters are not part of the command.

#### **Command Descriptions**

Command:

I (Input command)

or IO

(Input Override command)

Syntax:

I{b(o)(d)(/) }... IO{b(o)(d)(/) }...

Purpose:

The Input command specifies the data to be input, the order in which it is be input, and any masks which are to be overlaid onto the data prior to reporting it. The Input Override command provides the capability to read a different input sequence one time, without destroying the last defined I command input sequence.

Description:

I input command

10 input override

b one to six digits which specify the byte number, '0' through '5', or '\*' for all bytes.

o one of the following:

& AND the data specified by (d) to the specified input byte(s).

# OR the data specified by (d) to the specified input byte(s).

X XOR the data specified by (d) to the specified input byte(s).

d ASCII mask value '00' through 'FF' (required with 'o')

/ an optional character which is allowed to make the command more readable.

Default: I\* (input all bytes)

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically redefined by another I command, or by a Reset or Self Test command. Input can be requested for both input and output bytes.

Typical use of the I command simply defines a sequence of bytes to be read, with the sequence defined by the order of the digits following the I command. For example, 'I123' specifies that the data from bytes 1, 2, and 3 are to be reported in the order of byte 1 first, byte 2 second, and byte 3 third (followed by <CR><LF>).

Additional input of the same sequence does not require redefining the I command. Successive reads from the module will return new data in the defined sequence, each terminated by <CR> <LF>.

For example, 'I321' specifies an input sequence of 3-2-1. If bytes 1, 2, and 3 contained 11, 22, and 33 hex, the module would report '332211 < CR > < LF > ' when read. Subsequent reads of the module will report the update state of bytes 3, 2, and 1.

An '\*' in the I command automatically defines the byte sequence to be 0-1-2-3-4-5.

Each time an I command is issued, it defines a new input sequence. The input override command (IO) is used to look at a specific byte(s) without affecting the I command's sequence, as shown in the example below. Once the I command has been issued, its setup and sequence (including masks) remain valid until overridden by another I command, a QR or QD command, or reset or self test.

If external Data Ready Strobe has been defined as the condition to latch input data into the card, and no strobe has been received since the last input request, an 'N<CR><LF>' will be returned for both the I and IO commands, indicating no new data is available.

The state of the data returned represents the logic sense programmed with the mode (M) command.

If an I command is issued with no arguments ( (b) is omitted), the sequence will be cleared and the module will respond with a <CR><LF> only. If (o) and (d) are omitted, the command specifies data in its new input form. If (o) is specified without (d), an Invalid Input Command error will be generated. If any error is queued, the module will respond with a QE<CR><LF> on the subsequent input requests.

NOTE: All responses from the I and IO commands are terminated in <CR><LF>.

#### Example:

The example cases on the following page show how a sequence of I commands and implicit inputs will be reported (each case assumes the I/O lines are at 00, 11, 22, 33, 44, and 55 for bytes 0 to 5 respectively):

3 - 6 VX4801

| Case | Command                 | Byte<br>Sequence | Module Response                 |

|------|-------------------------|------------------|---------------------------------|

| 1    | Power-up State          | 0-1-2-3-4-5      | 001122334455 <cr><lf></lf></cr> |

| 2    | I123 <lf></lf>          | 1-2-3            | 112233 < CR > < LF >            |

| 3    | read (no I command)     | 1-2-3            | 112233 < CR > < LF >            |

| 4    | *&55 <cr><lf></lf></cr> | 0-1-2-3-4-5      | 001100114455 < CR > < LF >      |

| 5    | read (no I command)     | 0-1-2-3-4-5      | 001100114455 < CR > < LF >      |

| 6    | 1*;                     | 0-1-2-3-4-5      | 001122334455 < CR > < LF >      |

| 7    | IO3X11;                 | 3                | 22 < CR > < LF >                |

| 8    | read (no I command)     | 0-1-2-3-4-5      | 001122334455 < CR > < LF >      |

| 9    | 1543012;                | 5-4-3-0-1-2      | 554433001122 <cr><lf></lf></cr> |

| 10   | IO#55/1XAA/2345;        | 0-1-2-3-4-5      | 55BB22334455 < CR > < LF >      |

Case 1 is the initial default condition.

Case 2 requests the input from bytes 1, 2, and 3 in that order.

Case 3 reports the data from the input sequence set up in case 2.

Case 4 masks (ANDs) each input byte with a 55 hex prior to reporting it.

Case 5 reports the data using the sequence and mask set up in case 4.

Case 6 overrides the mask from case 4 and reports the data in its raw form.

Case 7 uses the override command to look at byte 3 XOR'd with an 11 hex.

Case 8 reports the data from the sequence defined in case 6.

Case 9 reports the data in the newly defined sequence 543012.

Case 10 reports the data in the newly defined sequence 012345, ORs byte 0 with a 55 hex, XORs byte 1 with an AA hex, and reports bytes 2, 3, 4, and 5 in their raw form. The "/" is used to make the command more readable.

Command:

L (Load Output)

or LO (Load Override output)

Syntax:

L{b(o)(d)(/) }... LO{b(o)(d)(/) }...

Purpose:

The Load Output command specifies the data bytes to be output, the sequence in which it is be output, and any masks which are to be overlaid onto the data prior to output by the module. The Load Override command provides the capability to output a different sequence of bytes one time, without destroying the last defined L command output sequence.

#### Description:

- L load output command

- LO load override

- b one to six digits which specify the byte number, 0 through 5, or \* for all bytes.

- o one or more of the following letters which specify various parameters:

- D Load the data specified by (d) to the specified output byte(s).

- S Set the bit indicated by (d) to a logic high (the eight bits of a byte are defined as '00' through '07', with bit '00' being the least significant bit).

- R Reset the bit indicated by (d) to a logic low (the eight bits of a byte are defined as '00' through '07', with bit '00' being the least significant bit).

- & AND the data specified by (d) to the specified output byte(s).

- # OR the data specified by (d) to the specified output byte(s).

- X XOR the data specified by (d) to the specified output byte(s).

- d ASCII value '00' through 'FF' (required with 'o'). Note that d is an 8-bit wide byte value if the 'o' parameter is a D, \$, or X, and a bit number if the 'o' parameter is an S or R.

- optional character allowed to make the command more readable.

Default: NONE (all bytes are initially defined as inputs (M command), set to TTL logic 0, and tri-stated (T command) ).

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically overridden by another L command, by redefining the I/O configuration (M command), or by a reset or self test command. If any bytes are not programmed, they will remain in their default (or previously programmed) state. The Set, Reset, and Mask parameters (S, R, X, #, and &) all operate on the last data output to a byte(s), and are valid only for the current command.

Typical use of the L command specifies an output byte and the data to be output. For example, 'L2D55' specifies that a '55' hex is to be output to byte 2.

Once an output sequence has been defined with the L command, ASCII hex data (00 - FF) may be written to the module without additional L commands. The order in which the outputs were specified in the last Load command defines an

output sequence. For example, 'L321D55' specifies that a '55' is to be output to bytes 3, 2, and 1. This command also defines the output sequence to be bytes 3-2-1. ASCII hex data sent to the module will then be buffered until the amount of data received matches the amount required by the output sequence. All bytes are thus physically updated at the same time when the total amount of data is received. In this example, six ASCII hex bytes are required since two bytes are required for each output byte. If '123456' were then sent to the card, byte 3 would be loaded with '12', byte 2 with '34', and byte 1 with "56", to match the 3-2-1 sequence. If an L command had not been previously issued, this data would be ignored.

An '\*' automatically defines the sequence 0-1-2-3-4-5.

Each time an L command is issued, it defines a new output sequence. The Load Override (LO) command is used to change specific data without affecting the L command's sequence, as shown in the examples below. Note that whenever a new L command is issued, any buffered data in an incompleted buffer is lost. The output sequence is also cleared whenever a new Mode (M) command is issued.

Note that a particular byte should only be defined once within the "L" command, because it can appear only once in the sequence. If a byte is defined more than once within the command, only the last specified action is taken. For example, 'LOD55/0D44' would load a 44 hex into byte 0 (the load 55 hex action is ignored). Similarly, 'LOS01/0S03' would only set bit 3 of byte 0. Setting both bits can be accomplished by using the mask command 'L0#05'.

The byte(s) will be physically output based on the conditions defined by the U command.

If output is commanded to a byte which is defined as an input (M command), an error will be flagged, and the command ignored. If the (b) parameter is omitted, the command will have <u>no</u> effect. The (o) and (d) parameters are optional. However, if (o) is specified without (d), an Invalid Hex Value error will be generated. If an invalid parameter is specified, an Invalid Load Command error will be generated.